## JAWAHARLAL COLLEGE OF ENGINEERING AND TECHNOLOGY

(Approved by AICTE, Affiliated to APJ Abdul Kalam Technological University, Kerala)

#### DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

(NBA Accredited)

# COURSE MATERIAL

# CST 202 COMPUTER ORGANIZATIONS AND ARCHITECTURE

### VISION OF THE INSTITUTION

Emerge as a centre of excellence for professional education to produce high quality engineers and entrepreneurs for the development of the region and the Nation.

### MISSION OF THE INSTITUTION

- To become an ultimate destination for acquiring latest and advanced knowledge in the multidisciplinary domains.

- To provide high quality education in engineering and technology through innovative teaching-learning practices, research and consultancy, embedded with professional ethics.

- To promote intellectual curiosity and thirst for acquiring knowledge through outcome based education.

- To have partnership with industry and reputed institutions to enhance the employability skills of the students and pedagogical pursuits.

- To leverage technologies to solve the real life societal problems through community services.

## **ABOUT THE DEPARTMENT**

- ➢ Established in: 2008

- > Courses offered: B.Tech in Computer Science and Engineering

- > Affiliated to the A P J Abdul Kalam Technological University.

#### **DEPARTMENT VISION**

To produce competent professionals with research and innovative skills, by providing them with the most conducive environment for quality academic and research oriented undergraduate education along with moral values committed to build a vibrant nation.

#### **DEPARTMENT MISSION**

- Provide a learning environment to develop creativity and problem solving skills in a professional manner.

- Expose to latest technologies and tools used in the field of computer science.

- Provide a platform to explore the industries to understand the work culture and expectation of an organization.

- Enhance Industry Institute Interaction program to develop the entrepreneurship skills.

- Develop research interest among students which will impart a better life for the society and the nation.

#### PROGRAMME EDUCATIONAL OBJECTIVES

Graduates will be able to

- Provide high-quality knowledge in computer science and engineering required for a computer professional to identify and solve problems in various application domains.

- Persist with the ability in innovative ideas in computer support systems and transmit the knowledge and skills for research and advanced learning.

- Manifest the motivational capabilities, and turn on a social and economic commitment to community services.

#### **PROGRAM OUTCOMES (POS)**

JCET

#### **Engineering Graduates will be able to:**

1. **Engineering knowledge**: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

2. **Problem analysis**: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

3. **Design/development of solutions**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

4. **Conduct investigations of complex problems**: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

5. **Modern tool usage**: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

6. **The engineer and society**: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

7. Environment and sustainability: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

8. **Ethics**: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

9. **Individual and team work**: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

10. **Communication**: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

11. **Project management and finance**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

12. **Life-long learning**: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

#### **COURSE OUTCOMES**

| SUBJECT CODE: C210 |                                                                                 |  |  |  |

|--------------------|---------------------------------------------------------------------------------|--|--|--|

|                    | COURSE OUTCOMES                                                                 |  |  |  |

| C210.1             | To identify the basic structure and functional units of a digital computer. And |  |  |  |

|                    | analyze the effect of addressing modes on the execution time of a program       |  |  |  |

| C210.2             | To design processing unit using the concepts of ALU and control logic design.   |  |  |  |

| C210.3             | To select appropriate interfacing standards for I/O devices.                    |  |  |  |

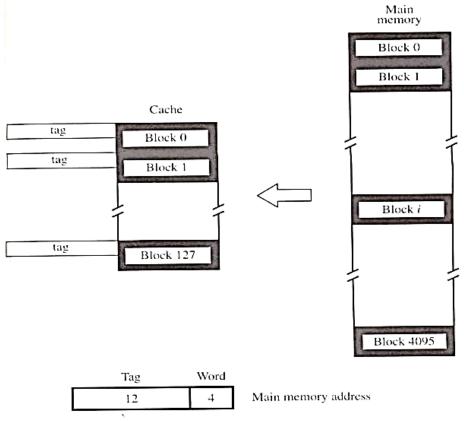

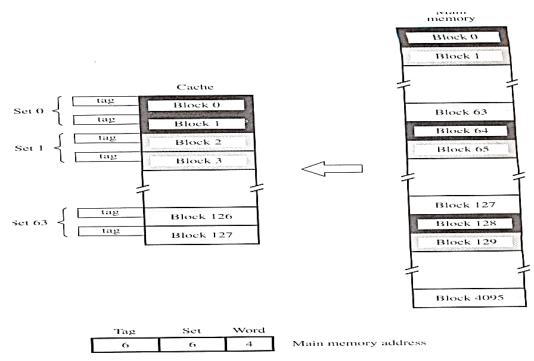

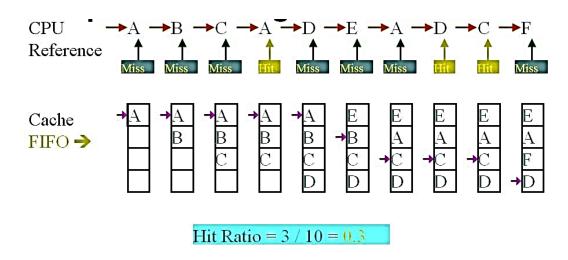

| C210.4             | To identify the pros and cons of different types of Memory systems and          |  |  |  |

|                    | understand mapping functions.                                                   |  |  |  |

| C210.5             | To select appropriate interfacing standards for I/O devices.                    |  |  |  |

| C210.6             | To identify the roles of various functional units of a computer in instruction  |  |  |  |

|                    | execution. And analyze the types of control logic design in processors.         |  |  |  |

#### **PROGRAM SPECIFIC OUTCOMES (PSO)**

The students will be able to

- Use fundamental knowledge of mathematics to solve problems using suitable analysis methods, data structure and algorithms.

- Interpret the basic concepts and methods of computer systems and technical specifications to provide accurate solutions.

- Apply theoretical and practical proficiency with a wide area of programming knowledge, design new ideas and innovations towards research.

#### **CO PO MAPPING**

| CO'S   | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| C210.1 | 3   | 2   | 2   | -   |     | -   | -   | -   | -   | -    | -    | 2    |

| C210.2 | 3   | 3   | -   | -   | 2   | -   | -   | -   | -   | -    | -    | 2    |

| C210.3 | 3   | 2   | -   | -   | 2   | -   | -   | -   | -   | -    | -    | 2    |

| C210.4 | 3   | 2   | 2   | -   |     | -   | -   | -   | -   | -    | -    | 2    |

| C210.5 | 3   | 3   | 3   | -   | -   | -   | -   | -   | -   | -    | -    | -    |

| C210.6 | 3   | 2   | -   | -   | 2   | -   | -   | -   | -   | -    | -    | 2    |

| C210   | 3   | 2.3 | 2.3 |     | 2   |     |     |     |     |      |      | 2    |

Note: H-Highly correlated=3, M-Medium correlated=2,L-Less correlated=1

#### **CO PSO MAPPING**

| CO'S   | PSO1 | PSO2 | PSO3 |

|--------|------|------|------|

| C210.1 | 3    | 2    | 2    |

| C210.2 | 3    | 2    | 2    |

| C210.3 | 3    | 2    | 2    |

| C210.4 | 2    | 2    | 2    |

| C210.5 | 2    | 3    | 2    |

| C210.6 | 2    | 3    | 2    |

| C210   | 2.5  | 2.3  | 2    |

| S:NO | TOPIC                                               |

|------|-----------------------------------------------------|

| 1    | Von Neumann architecture                            |

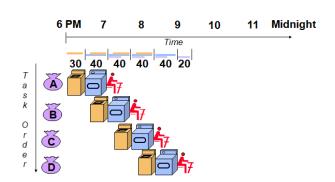

| 2    | Computer Organization and Architecture   Pipelining |

# **Reference Materials**

# MODULE - I

Basic Structure of computers – functional units - basic operational concepts - bus structures. Memory locations and addresses - memory operations, Instructions and instruction sequencing, addressing modes. Basic processing unit – fundamental concepts – instruction cycle – execution of a complete instruction single bus and multiple bus organization

**Computer Organization:** It refers to the operational units and their interconnections that realize the architectural specifications.

The components from which computers are built, i.e., computer organization.

It describes the function of and design of the various units of digital computer that store and process information.

**Computer Architecture:** It is concerned with the structure and behaviour of the computer. It includes the information formats, the instruction set and techniques for addressing memory. Computer architecture is the science of integrating those components to achieve a level of functionality and performance.

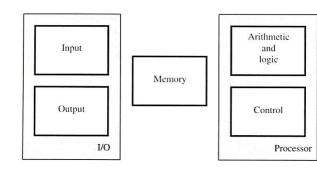

## Functional units of a Computer

A computer consists of 5 main parts.

- 1. Input

- 2. Memory

- 3. Arithmetic and logic

- 4. Output

- 5. Control Units

#### Basic functional units of a computer.

### Input Unit:

- Computers accept coded information through input units, which read the data.

- Whenever a key is pressed, the corresponding letter or digit is automatically translated into its corresponding binary code and transmitted over a cable to either the memory or the processor.

- Some input devices are Keyboard, Joysticks Trackballs Mouse Microphones

#### **Output Unit:**

- Its function is to send the processed results to the outside world. eg.Printer

- Printers are capable of printing 10000 lines per minute but its speed is comparatively slower than the processor.

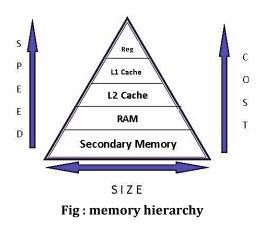

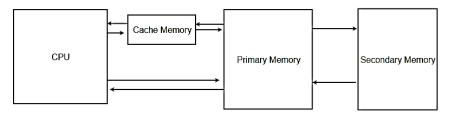

## **Memory Unit:**

- It stores the programs and data.

- There are 2 types of storage classes Primary Secondary

## **Primary Storage:**

- It is a fast memory that operates at electronic speeds.

- Programs must be stored in the memory while they are being executed.

- The memory contains large no of semiconductor storage cells.

- Each cell carries 1 bit of information.

- The Cells are processed in a group of fixed size called Words.

- To provide easy access to any word in a memory, a distinct address is associated with each word location.

- Addresses are numbers that identify successive locations.

- The number of bits in each word is called the word length.

- The word length ranges from 16 to 64 bits.

### ALU:

- Most computer operations are executed in ALU.

- Consider a example, Suppose 2 numbers located in memory are to be added. They are brought into the processor and the actual addition is carried out by the ALU. The sum may then be stored in the memory or retained in the processor for immediate use.

- Access time to registers is faster than access time to the fastest cache unit in memory.

## **Control Unit:**

- The operations of Input unit, output unit, ALU are co-ordinate by the control unit.

- The control unit is the Nerve centre that sends control signals to other units and senses their states.

- Data transfers between the processor and the memory are also controlled by the control unit through timing signals.

- The operation of computers are,

- The computer accepts information in the form of programs and data through an input unit and stores it in the memory.

- Information stored in the memory is fetched, under program control into an arithmetic and logic unit, where it is processed.

- Processed information leaves the computer through an output unit.

- All activities inside the machine are directed by the control unit.

## 2. Basic operational concepts

JCET

To execute a given task as per the appropriate program, Program consists of list of instructions stored in memory

The individual instructions are brought from the memory to the processor, which executes the specified operation.

In order to execute an operation in a processor the required instructions have to be brought out from the memory to the processor.

Transfers between memory and processor are started by sending the address of the memory location to be accessed to the memory unit and issuing the appropriate control signals.

Then the data are transferred to or from the memory.

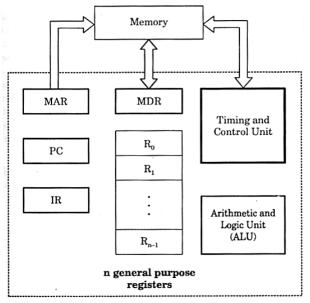

Registers are fast stand-alone storage locations that hold data temporarily. Multiple registers are needed to facilitate the operation of the CPU. Some of these registers are

- Instruction register (IR) : Hold the Instructions that is currently being executed

- Program Counter (PC): It contains the memory address of the next instruction to be fetched for execution.

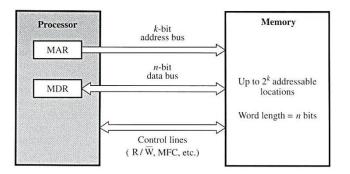

- **Memory Address Register (MAR)** and **Memory Data Register (MDR)**: These are the two registers which are facilitating the communication between the processor and memory.

**Read Operation :** In order to read an information from memory **the address** of the memory location in which the information is residing have to be **put in MAR** and a **Read control signal** will be sent to memory unit. When the memory unit sees the address in address line of the bus and read signal in control line of the bus memory will start the read operation from the concerned address and the **result will be sent to the MDR**.

*Write operation* : Initially the **data** to be written into the memory has to be **placed in MDR** and the **address** in which the desired information have to be kept in memory will be **placed in MAR** and a **Write control signal** will be sent to the memory unit. When the memory unit sees the address, data and writes signal in the external memory bus it will start the corresponding write operation.

#### Execution of instructions:

JCET

- The contents of PC transferred to MAR

- Select a particular memory location

- Issues RD control signals

- Reads instruction present in memory and loaded into MDR will be placed in IR (Contents transferred from MDR to IR)

- Instruction present in IR will be decoded by which processor understand what operation it has to perform

- Increments the contents of PC by 1, so that it points to the next instruction address

- If data required for operation is available in register, it performs the operation

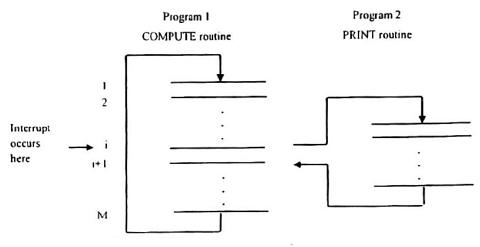

**Note :** Normal execution of the program may be pre-empted if some device requires urgent servicing. In order to deal with the situation immediately, the normal execution of the current program may be interrupted.

The processor provides the requested service called the **Interrupt Service Routine (ISR)**. Contents of PC, general registers, and some control information are stored in memory. When ISR is completed, the state of the processor is restored and the interrupted program may continue its execution.

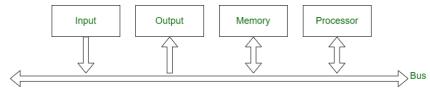

## 3. Bus Structure

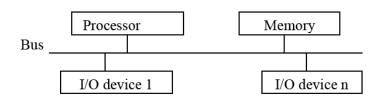

A group of lines that serves as the connection path to several devices is called a Bus.

There are 2 types of Bus structures. They are

- Single Bus Structure

- Multiple Bus Structure

### **Single Bus Structure**

Single Bus Structure

- Common bus used to communicate between peripherals and microprocessor

- It allows only one transfer at a time.

- It costs low.

- It is flexible for attaching peripheral devices.

- Its Performance is low.

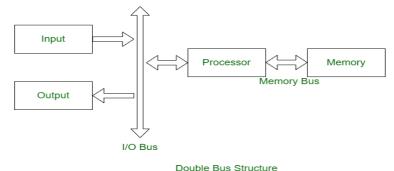

## **Multiple Bus Structure**

JCET

It is to overcome the bottleneck of single bus structure.

- To improve performance multibus structure can be used

- It allows two or more transfer at a time.

- It costs high.

- It provides concurrency in operation.

- Its Performance is high.

- In two bus structure: One bus can be used to fetch instruction other can be used to fetch data, required for execution, thus improving the performance, but cost increases.

| Single Bus Structure                                                        | Double Bus Structure                                                                |  |  |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|

| One common bus is used for communication between peripherals and processor. | Two buses are used, one for communication from peripherals and other for processor. |  |  |

| Instructions and data both are transferred in same bus.                     | Instructions and data both are transferred in different buses.                      |  |  |

| Its performance is low.                                                     | Its performance is high.                                                            |  |  |

| Cost of single bus structure is low.                                        | Cost of double bus structure is high.                                               |  |  |

| Number of cycles for execution is more.                                     | Number of cycles for execution is less.                                             |  |  |

| Execution of process is slow.                                               | Execution of process is fast.                                                       |  |  |

| Number of registers associated is less.                                     | Number of registers associated is more.                                             |  |  |

| At a time single operand can be read from bus.                              | At a time two operands can be read.                                                 |  |  |

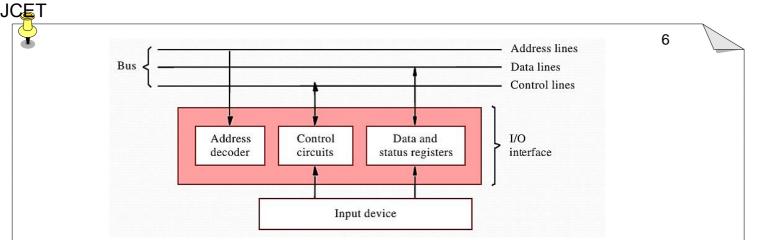

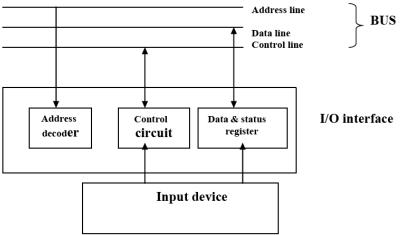

The bus consists of three set of lines used to carry address, data and control signals known as *data bus*, *address bus* and *control bus*.

- **Address bus:** *unidirectional:* group of wires which carries *address information bits* form processor to peripherals.

- Data bus: *bidirectional* : group of wires which carries *data information bit* form processor to peripherals and vice – versa

- Control bus: *bidirectional*: group of wires which carries *control signals* form processor to peripherals and vice – versa

- Above figure shows the input device interface to the bus.

- Each I/O device is assigned a unique set of addresses for the registers in its interface.

- When the processor places a particular address on the address lines, it is examined by the address decoders of all devices on the bus.

- The device that recognizes this address responds to the commands issued on the control lines.

- The processor uses the control lines to request either a Read or a Write operation, and the requested data are transferred over the data lines.

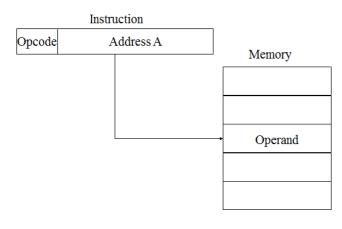

## 4. Memory locations and addresses

- **Main memory** is the second major subsystem in a computer. It consists of a collection of storage locations, each with a unique identifier, called an **address**.

- Data is transferred to and from memory in groups of bits called **words**. A word can be a group of 8 bits, 16 bits, 32 bits or 64 bits (and growing).

| Memory units |                                       |                        |  |  |

|--------------|---------------------------------------|------------------------|--|--|

| Unit         | Exact Number of Bytes                 | Approximation          |  |  |

| kilobyte     | 2 <sup>10</sup> (1024) bytes          | 10 <sup>3</sup> bytes  |  |  |

| megabyte     | 2 <sup>20</sup> (1,048,576) bytes     | 10 <sup>6</sup> bytes  |  |  |

| gigabyte     | 2 <sup>30</sup> (1,073,741,824) bytes | 10 <sup>9</sup> bytes  |  |  |

| terabyte     | 2 <sup>40</sup> bytes                 | 10 <sup>12</sup> bytes |  |  |

- A computer has 32 MB (megabytes) of memory. How many bits are needed to address any single byte in memory?

- The memory address space is 32 MB, or  $2^{25}$  ( $2^5 \times 2^{20}$ ). This means that we need  $\log_2 2^{25}$ , or **25 bits**, to address each byte.

- A computer has 128 MB of memory. Each word in this computer is eight bytes. How many bits are needed to address any single word in memory?

- The memory address space is 128 MB, which means 2<sup>27</sup>. However, each word is eight (2<sup>3</sup>) bytes, which means that we have 2<sup>24</sup> words. This means that we need log<sub>2</sub> 2<sup>24</sup>, or **24 bits**, to address each word.

JCET

- Little Endian: low order byte stored at lowest address

- Eg: CD12AB90 (32 bit data)

H BYTE 🔶 L BYTE

| Address | Value |

|---------|-------|

| 1000    | 90    |

| 1001    | AB    |

| 1002    | 12    |

| 1003    | CD    |

- e.g., e.g., in DEC, Intel

- Big Endian: high order byte stored at lowest address

- Eg: CD12AB90 (32 bit data)

| Address | Value |

|---------|-------|

| 1000    | CD    |

| 1001    | 12    |

| 1002    | AB    |

| 1003    | 90    |

## 5. Memory operations

- Both program instructions and data operands are stored in the memory.

- To execute an instruction, the instruction to be transferred from the memory to the processor.

- Operands and results must also be moved between the memory and the processor.

- Two basic operations requires in memory access

- Load operation (Read or Fetch):

- The Load operation transfers a copy of the contents of a specific memorylocation to the processor.

- The memory contents remain unchanged.

- Steps for Load operation:

- 1) Processor sends the address of the desired location to the memory.

- 2) Processor issues "read" signal to memory to fetch the data.

- 3) Memory reads the data stored at that address.

- 4) Memory sends the read data to the processor.

- Store operation (Write):

- The Store operation transfers the information from the register to the specified memory-location.

- This will destroy the original contents of that memory-location.

- Steps for Store operation are:

1) Processor sends the address of the memory-location where it wants to store data.

2) Processor issues ",write" signal to memory to store the data.

3) Content of register (MDR) is written into the specified memory-location.

## 6. Instructions and instruction sequencing

- A computer must have instruction capable of performing the following operations. They are

- Data transfer between memory and processor register.

- Arithmetic and logical operations on data.

- Program sequencing and control.

- $\circ$  I/O transfer.

- Complete instruction set of the processor is called instruction set architecture.

- The possible locations in which transfer of information occurs are,

- Memory Location (LOC,PLACE,MEM are the address of memory location)

- Processor register (R1 , R2,... are processor registers)

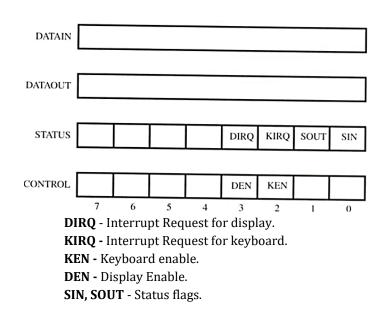

- Registers in I/O sub-system (DATA\_IN, DATA\_OUT are I/O registers)

- Contents of location is indicated by using square brackets []

- Assembly Language Notation

- Use Mnemonics

- Eg:

MOVE LOC, R1 - Transfers the contents of memory location to the processor register R1

ADD R1,R2,R3 - Add the contents of register R1 & R2 and places their sum into register R3.

### • Type of Instructions

- Three address instruction

- Syntax: Operation source 1, source 2, destination

- Eg: ADD D,E,F where D,E,F are memory location

- Advantage: Single instruction can perform the complete operation

- Disadvantage : Instruction code will be too large to fit in one word location in memory

- Two Address Instruction

- Syntax : Operation source, destination

- Eg: MOVE E,F

ADD D, F

Perform ADD A,B,C using 2instructions

MOVE B, C

ADD A, C

Disadvantage: Single instruction is not sufficient to perform the entire operation.

- o One Address Instruction

- Syntax- Operation source/destination

- In this type either a source or destination operand is mentioned in the instruction

- Other operand is implied to be a processor register called Accumulator

- Eg: ADD B

- Perform ADD D,E,F

- Load D

- ADD E

STORE F

- Zero address instruction

- Syntax : Operation source

- Location of all operands are defined implicitly

- Ex: CLA is a 0-address instruction, CLA stands for clear accumulator.

- Branch instruction is those which change the normal sequence of execution.

- We have conditional branch instructions and unconditional branch instruction.

- Unconditional branch instruction changes the sequence of execution irrespective of condition of the results.

- Example : JMP 2000 Jumps to the address 2000

- Conditional branch instruction changes the sequence only when certain conditions are met.

- Example :

- JNC 3000 Jumps to the address if carry flag is 0

- JZ 2000 Jumps to the address if zero flag is 1

- **Conditional Code Flags**: The processor keeps track of information about the results of various operations for use by subsequent conditional branch instructions

- N Negative 1 if results are Negative

- 0 if results are Positive

- Z Zero 1 if results are Zero

- 0 if results are Non zero

- V Overflow 1 if arithmetic overflow occurs

0 non overflow occurs

- C Carry 1 if carry and from MSB bit

- 0 if there is no carry from MSB bit

# 7. Addressing Modes

JCET

The different ways in which the location of the operand is specified in an instruction are referred to as addressing modes

- 1. Immediate Addressing

- 2. Direct Addressing

- 3. Indirect Addressing

- 4. Register Addressing

- 5. Register Indirect Addressing

- 6. Indexed Addressing

- 7. Relative Addressing

## **Immediate Addressing**

- Operand is given explicitly in the instruction

- Operand = Value

- e.g. ADD 5

- Add 5 to contents of accumulator

- 5 is operand

- No memory reference to fetch data

- Fast

- Limited range

| Instruction |         |  |  |  |

|-------------|---------|--|--|--|

| opcode      | operand |  |  |  |

|             | operand |  |  |  |

## **Direct Addressing**

- Address field contains address of operand

- Effective address (EA) = address field (A)

- e.g. ADD A

- Add contents of cell A to accumulator

- Look in memory at address A for operand

- Single memory reference to access data

- No additional calculations to work out effective address

- Limited address space

11

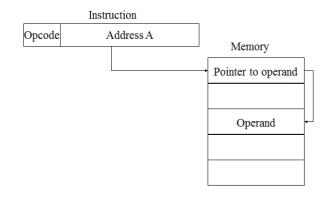

### **Indirect Addressing**

JCET

- Memory cell pointed to by address field contains the address of (pointer to) the operand

- EA = [A]

.

- Look in A, find address (A) and look there for operand

- e.g. ADD (A)

- Add contents of cell pointed to by contents of A to accumulator

- Large address space

- 2<sup>n</sup> where n = word length

- May be nested, multilevel, cascaded

- e.g. EA = (((A)))

- Draw the diagram yourself

- Multiple memory accesses to find operand

- Hence slower

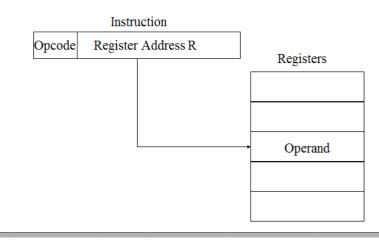

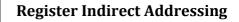

### **Register Addressing**

- Operand is held in register named in address field

- EA = R

- Limited number of registers

- Very small address field needed

- Shorter instructions

- Faster instruction fetch

- No memory access

- Very fast execution

- Very limited address space

- Multiple registers helps performance

- Requires good assembly programming or compiler writing

- C.f. indirect addressing

- EA = [R]

JCET

- Operand is in memory cell pointed to by contents of register R

- Large address space (2<sup>n</sup>)

- One fewer memory access than indirect addressing

- Instruction

Opcode Register Address R

Memory

Registers

Pointer to Operand

Operand

Operand

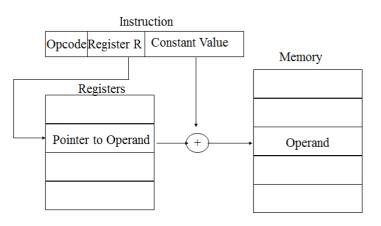

#### **Indexed Addressing**

- EA = X + [R]

- Address field hold two values

- X = constant value (offset)

- R = register that holds address of memory locations

- or vice versa

(Offset given as constant or in the index register)

Add 20(R1),R2 or Add 1000(R1),R2

#### **Relative Addressing**

- A version of displacement addressing

- R = Program counter, PC

- EA = X + (PC)

- i.e. get operand from X bytes away from current location pointed to by PC.

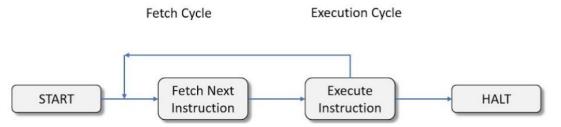

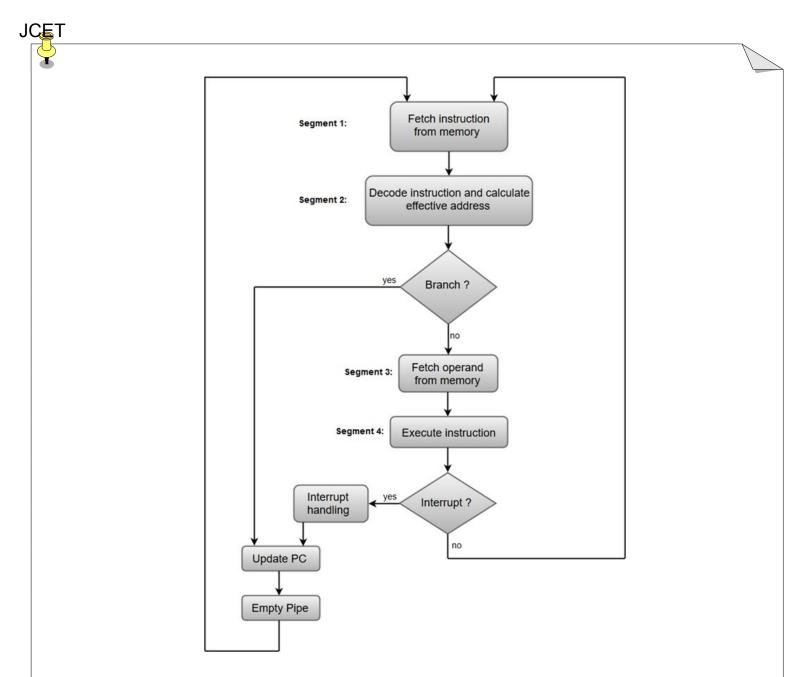

## 8. Instruction cycle

- The basic function performed by a computer is execution of a program, which consists of a set of instructions stored in memory.

- The processor does the actual work by executing instructions specified in the program.

- In the simplest form, instruction processing consists of two steps: the processor reads (fetches) instructions from memory one at a time and executes each instruction.

- The processing required for a single instruction is called an *instruction cycle*.

An instruction cycle is shown below:

- Program execution halts only if the machine is turned off, some sort of unrecoverable error occurs, or a program instruction that halts the computer is encountered.

- Instruction Fetch and Execute

- The processor fetches an instruction from memory program counter (PC) register holds the address of the instruction to be fetched next.

- The processor increments the PC after each instruction fetch so that it will fetch the next instruction in the sequence.

- The fetched instruction is loaded into the instruction register (IR) in the processor the instruction contains bits that specify the action the processor will take.

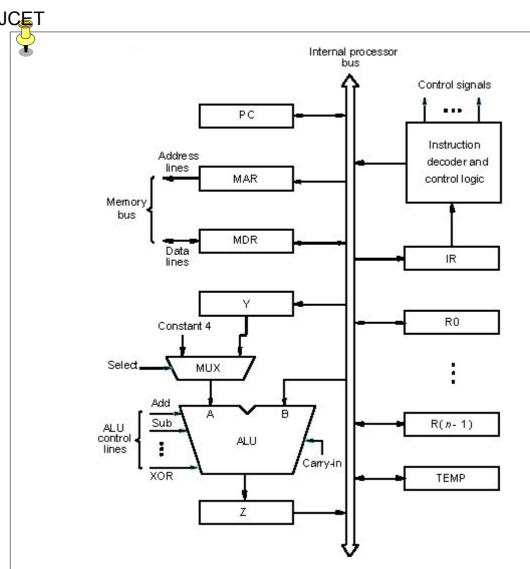

## 9. Single Bus Organization

- In this section we are dealing with how the instructions are processed within the processing unit.

- The ALU registers and the internal processor bus together known as datapath.

Figure: Single-bus organization of the datapath inside a processor

Normally in the instruction execution following operations may be happen in different sequences:

- Register transfer

- > Performing an arithmetic and logic operation

- Fetching a word from memory

- Storing a word in memory

#### **Register transfer :**

Example : Transfer the contents of register R1 to R4.

- Set  $R_{1out}$  to 1. This places the contents of R1 to the bus.

- $\bullet$  set  $R_{4in}$  to 1. This loads data from the processor bus to register R4

#### Performing an arithmetic and logic operation

Example : SUB R4,R5,R6 Subtract the contents of R4 from R5 and store the result in R6.

- R<sub>4out</sub>, Yin

- R<sub>5out</sub> ,Select Y ,sub, Z<sub>in</sub>

- Zout, R6in

### Fetching a word from memory

Example: MOVE [R1] , R2 R1out, MARin, READ MDR<sub>inE</sub>, WMFC MDRout, R2in

### Storing a word in memory

Example: MOVE R2, (R1) R1out,MARin R2out, MDRin, WRITE MDRout, WMFC

#### Execution of a complete instruction

Example : Add R2, R1

- Fetch the instruction

- Fetch the operands

- Perform the addition

- Load the result into R1

#### Step Action

- 1 PC<sub>out</sub>, MAR in , Read, Select4, Add, Zin

- 2 Z<sub>out</sub> , PC<sub>in</sub> , Y<sub>in</sub> , WMF C

- 3 MDR<sub>out</sub> , IR<sub>in</sub>

- 4 R1<sub>out</sub> , Y<sub>in</sub>

- 5 R2<sub>out</sub>, SelectY, Add, Z<sub>in</sub>

- 6 Z<sub>out</sub> , R1<sub>in</sub> , End

#### Example : Add (R3), R1

- Fetch the instruction

- Fetch the operands

- Perform the addition

- Load the result into R1

#### Step Action

- 1 PC<sub>out</sub> , MAR in , Read, Select4,Add, Zin

- 2 Z<sub>out</sub> , PC<sub>in</sub> , Y<sub>in</sub> , WMF C

- 3 MDR<sub>out</sub> , IR<sub>in</sub>

- 4 R3<sub>out</sub> , MAR in , Read

- 5 R1<sub>out</sub> , Y<sub>in</sub> , WMF C

- 6 MDR<sub>out</sub> , SelectY, Add, Z<sub>in</sub>

- 7 Zout , R1in , End

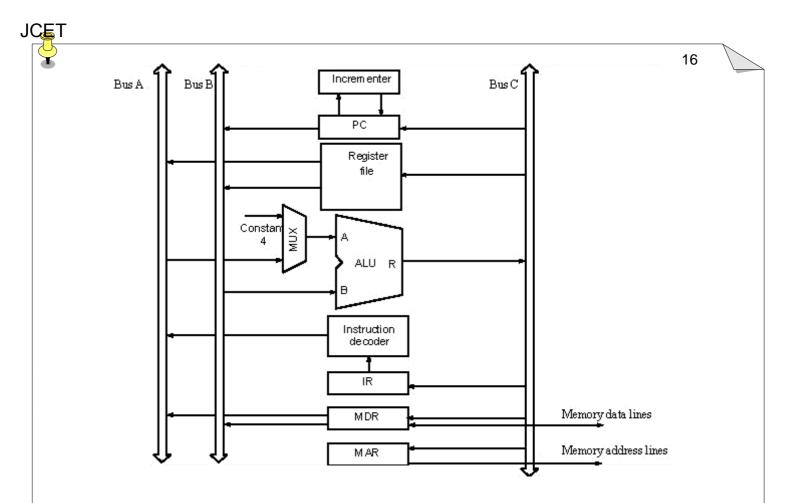

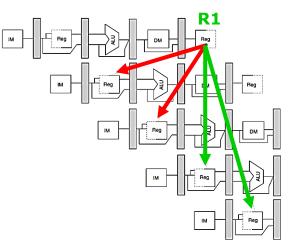

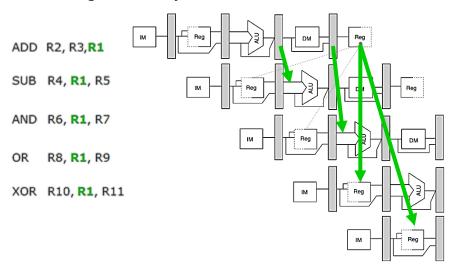

## **10.** Multiple Bus Organization

- Multiple bus more than one data word can be transferred over the bus in a clock cycle. This

increases the steps required to complete the execution of the instruction

- To reduce the number of steps needed to execute instructions, most commercial process provide multiple internal paths that enable several transfer to take place in parallel

- 3 buses are used to connect registers and the ALU of the processor. \_

- All general purpose registers are shown by a single block called register file. \_

- There are 3 ports, one input port and two output ports. So it is possible to access data of three register in one clock cycle, the value can be loaded in one register from bus C and data from two register can be accessed to bus A and bus B.

#### **Execution of a complete instruction**

Example Add D4 DE

| Example : Add R4, R5, R6 |                                                          |  |  |  |

|--------------------------|----------------------------------------------------------|--|--|--|

| Step                     | Action                                                   |  |  |  |

| 1                        | PC <sub>out</sub> , R=B, MAR <sub>in</sub> , Read, IncPC |  |  |  |

| 2                        | WMF C                                                    |  |  |  |

| 3                        | MDR <sub>outB</sub> , R=B, IR <sub>in</sub>              |  |  |  |

$\rm R4_{outA}$  ,  $\rm R5_{outB}$  , SelectA, Add,  $\rm R6_{in}, End$ 4

## **MODULE – II**

**Register transfer logic:** inter register transfer – arithmetic, logic and shift micro operations. **Processor logic design: -** processor organization – Arithmetic logic unit - design of arithmetic circuit - design of logic circuit - Design of arithmetic logic unit - status register – design of shifter - processor unit – design of accumulator.

## **REGISTER TRANSFER LOGIC:**

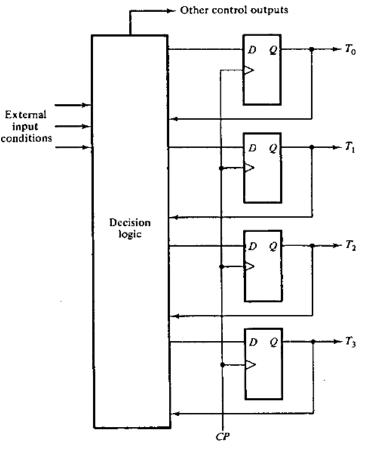

- Digital system is a collection of digital hardware modules.

- A digital system is a sequential logic system constructed with flip flops and gates. The sequential circuit can be specified by means of a state table.

- Specifying a large digital system with a state table would be very difficult, since the number of states would be very large.

- To overcome this difficulty, digital systems are designed using a modular approach, where each modular subsystem performs some functional task.

- The modules are constructed from such digital functions as registers, counters, decoders, multiplexers, arithmetic elements and control logic.

- Various modules are interconnected with data and control path.

- The interconnection of digital functions cannot be described by means of combinational or sequential logic techniques.

- The information flow and the processing task among the data stored in the registers can be described by means of **register transfer logic**.

- The registers are selected as primitive components of the system. Register transfer logic uses a set

of expressions and statements which compare the statements used in programming language.

- It provides the necessary tool for specifying the interconnection between various digital functions.

# > Components of Register Transfer Logic

- 1. *The set of registers in the system and their functions:* A register also encompasses all type of registers including shift registers, counters and memory units.

- 2. *The binary-coded information stored in the registers:* The binary information stored in registers may be binary numbers, binary coded decimal numbers, alphanumeric characters, control information or any other binary coded information.

- 3. *The operations performed on the information stored in the registers:* The operations performed on data stored in registers are called micro operations. Examples are shift, count, add, clear and load

- 4. *The control functions that initiate the sequence of operations:* The control functions that initiate the sequence of operations consists of timing signals that sequence the operations one at a time.

## > Register transfer language (Computer hardware description language)

- Symbolic notation used for registers, for specifying operations on the contents of registers and specifying control functions.

- A statement in a register transfer language consists of control function and a list of microoperations.

- Micro-Operation: Operations performed in data stored in registers. Elementary operation that can be performed parallel during one clock pulse period.

- The result of operation may replace the previous binary information of a register or may be transferred to another register. Example: Shift, count, clear, add & load

- A micro-operation requires one clock pulse for the execution if the operation done in parallel.

In serial computer a microoperation requires a number of clock pulses equal to the word time in the system.

## > Types of Micro-Operations in digital system

- 1. **Inter register transfer micro-operation:** Do not change the information content when the binary information moves from one register to another

- 2. Arithmetic operation: Perform arithmetic on numbers stored in registers.

- 3. **Logic microoperation:** Perform operations such as AND and OR on individual pairs of bits stored in registers.

- 4. Shift microoperation: Specify operations for shift registers.

- > Inter Register Transfer

- Registers are the primitive component.

- Computer registers are designated by capital letters (sometimes followed by numerals) to denote the function of the register.

Example:

R1 - Processor Register, MAR - Memory Address Register PC - Program Counter, IR - Instruction Register, SR: Status Register

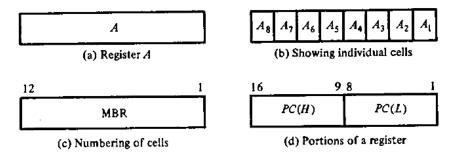

The cells or flip-flops of n-bit register are numbered in sequence from1 to n (from 0 to n-1) starting either from left or from right.

The register can be represented in 4 ways:

- Rectangular box with name of the register inside

- The individual cells is assigned a letter with a subscript number

- The numbering of cells from right to left can be marked on top of the box as the 12 bit register Memory Buffer Register (MBR).

- 16 bit register is partitioned into 2 parts, bits 1 to 8 are assigned the letter L(for low) and bits

9 to 16 are assigned the letter H(for high)

#### **Fig: Register Representations**

– Information transfer from one register to another is described by a **replacement operator**:

A ← B.

- This statement denotes a transfer of the content of register B into register A and this transfer happens in one clock cycle.

- After the operation, the content of the B (source) does not change. The content of the A (destination) will be lost and replaced by the new data transferred from B.

## > Conditional transfer occurs only under a control condition:

- The condition that determines when the transfer is to occurs called a **control function**.

- A control function is a Boolean function that can be equal to 1 or 0.

- The control function is included with the statement as follows

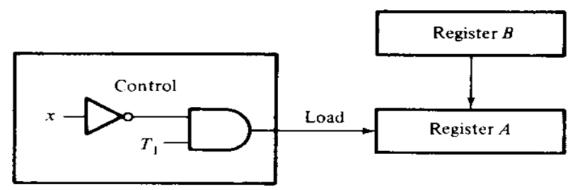

#### $x' T_1: A \leftarrow B$

- The control function is terminated with a colon.

- It symbolizes the requirement that the transfer operation be executed by the hardware only when the Boolean function  $x'T_1 = 1$ . ie; when variable x = 0 and timing variable  $T_1 = 1$ .

- Hardware implementation of a controlled transfer:  $x'T_1: A \leftarrow B$  is as follows

- The outputs of register B are connected to the input of register A and the number of lines in this connection is equal to the number of bits in the registers.

- Register A must have a load control input so that it can be enabled when the control function is 1.

- It is assumed that register A has an additional input that accepts continuous synchronized clock pulses.

- The control function is generated by means of an inverter and an AND gate.

- It is also assumed that the control unit that generates the timing variable T<sub>1</sub> i synchronized with the same clock pulses that are applied to register A.

- The control function stays on during one clock pulse period (when the timing variable is equal to 1) and the transfer occurs during the next transaction of a clock pulse.

- Destination register receives information from two sources but not at the same time.

- Consider an example

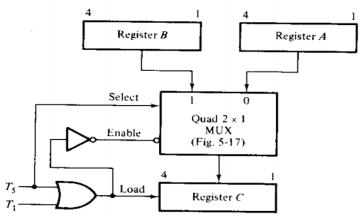

$T1 : C \leftarrow A$  $T5 : C \leftarrow B$

- The first line states that the contents of register A are to be transferred to register C when timing variable T<sub>1</sub> occurs.

- The second statement uses the same destination register C as the first but with a different source register and a different timing variable.

- The connections of two source registers to the same destination register cannot be done directly but requires a multiplexer circuit to select between the two possible paths.

The block diagram of the circuit that implements the two statements is shown in the figure.

- For registers with four bits each, we need a quadruple 2 to 1 line multiplexer in order to select either A or B. When  $T_5 = 1$ , register B is selected but when  $T_1=1$ , register A is selected (because  $T_5$  must be 0 when  $T_1$  is 1).

- The multiplexer and the load input of register C are enabled every time  $T_1$  and  $T_5$  occur.

- This causes a transfer of information from the selected source register to destination register.

| Symbol                | Description                              | Examples                         |

|-----------------------|------------------------------------------|----------------------------------|

| Letter (and Numerals) | Denotes a Register                       | A, MDR, R2                       |

| Subscript             | Denotes a bit of a Register              | A2, B6                           |

| Parenthesis ( )       | Denotes a portion of Register            | PC(H), MBR (OP)                  |

| Arrow ←               | Denotes transfer of information          | A ← B                            |

| Colon :               | Terminates a control function            | X'T <sub>0</sub> :               |

| Comma                 | Separates two micro-operations           | $A \leftarrow B, B \leftarrow A$ |

| Square Brackets [ ]   | Specifies an address for memory transfer | MBR ← M [ MAR ]                  |

# Conditional control statement

- Specify a control condition by a conditional statement rather than a Boolean control function

- Symbolised by if-then-else statement

## P: If (condition) then [microoperation(s)] else [microoperation(s)]

- As an example, consider the conditional control statement:

T2: If(C=0) then  $(F \leftarrow 1)$  else  $(F \leftarrow 0)$

F is assumed to be 1-bit register (flip-flop) that can be set or cleared.

If register C is a 1-bit register the statement is equivalent to the following statements

$$C'T_2: F \leftarrow 1 CT_2: F \leftarrow 0$$

## > Arithmetic Micro-Operations

The basic arithmetic micro-operations are:

- Addition

- Subtraction

- Increment

- Decrement

- Arithmetic shift

- The increment and decrement micro-operations are implemented with a combinational circuit or with a binary up-down counter as these micro-operations use plus-one and minus-one operation respectively.

- The arithmetic add microoperations are defined by the statement

$F \leftarrow A + B$

- It states that the contents of register A are to be added to the contents of register B and the sum is transferred to register F

- To implement this statement require 3 registers A, B and F and a digital function that performs the addition operation such as parallel adder.

| Symbolic<br>designation             | Description                                             |  |  |

|-------------------------------------|---------------------------------------------------------|--|--|

| $F \leftarrow A + B$                | Contents of A plus B transferred to F                   |  |  |

| $F \leftarrow A - B$                | Contents of $A$ minus $B$ transferred to $F$            |  |  |

| $B \leftarrow \overline{B}$         | Complement register B (1's complement)                  |  |  |

| $B \leftarrow \overline{B} + 1$     | Form the 2's complement of the contents of register $B$ |  |  |

| $F \leftarrow A + \overline{B} + 1$ | A plus the 2's complement of $B$ transferred to $F$     |  |  |

| $A \leftarrow A + 1$                | Increment the contents of A by 1 (count up)             |  |  |

| $A \leftarrow A - 1$                | Decrement the contents of $A$ by 1 (count down)         |  |  |

There must be a direct relationship between the statements written in a register transfer language and the registers and digital functions which are required for the implementation

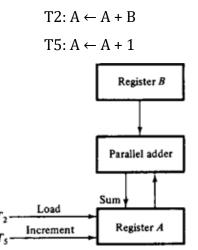

Consider the statements

- Timing variable T2 initiates an operation to add the contents of register B to the present contents of A with a parallel adder.

- Timing variable T5 increments register A with a counter.

- The transfer of the sum from parallel adder into register A can be activated with a load input in the register.

- Register be a counter with parallel load capability.

- The parallel adder receives input information from registers A and B.

- The sum bits from the parallel adder are applied to the inputs of A and timing variable T2 loads the sum into register A.

- Timing variable T5 increments there by enabling increment input register.

- Two basic arithmetic operations (multiplication and divide) are not included in the basic set of micro-operations.

- They are implemented by means of a combinational circuit.

- In general, the multiplication micro-operation is implemented with a sequence of add and shift micro- operations.

- Division is implemented with a sequence of subtract and shift micro-operations.

#### Logic Micro-Operations

- Logic micro-operations specify binary operations for strings of bits stored in registers.

- These operations consider each bit of the register separately and treat them as binary variables.

For example, the exclusive-OR micro-operation with the contents of two registers A and B is symbolized by the statement

- It specifies a logic micro-operation that considers each pair of bits in the registers as a binary variable.

- Let the content of register A is 1010 and the content of register B is 1100. The exclusive-OR microoperation stated above symbolizes the following logic computation:

- 1010 Content of A

- <u>1100</u> Content of B

- 0110 Content of  $F \leftarrow A \bigoplus B$

- The content of F, after the execution of the micro-operation, is equal to the bit-by-bit exclusive-OR operation on pairs of bits in B and values of A.

- The logic micro-operations are seldom used in scientific computations, but they are very useful for bit manipulation of binary data and for making logical decisions.

| Boolean<br>Functions                                                   | Operator<br>symbol | Name         | Comments            |

|------------------------------------------------------------------------|--------------------|--------------|---------------------|

| F <sub>0</sub> =0                                                      |                    | Null         | Binary constant 0   |

| F <sub>1</sub> =xy                                                     | x.y                | AND          | x and y             |

| F2=xy'                                                                 | x/y                | Inhibition   | x but not y         |

| F <sub>3</sub> =x                                                      |                    | Transfer     | x                   |

| F₄=x`y                                                                 | y/x                | Inhibition   | y but not x         |

| F₅≕y                                                                   |                    | Transfer     | Y                   |

| F <sub>6</sub> =xy'+x'y                                                | x⊕y                | Exclusive-OR | x or y but not both |

| $F_{\tau} = x + y$                                                     | x + y              | OR           | x or y              |

| $F_{g}=(x+y)'$                                                         | хĮу                | NOR          | Not-OR              |

| $\mathbf{F}_{9} = \mathbf{x}\mathbf{y} + \mathbf{x}^{*}\mathbf{y}^{*}$ | х Өу               | Equivalence  | x equals y          |

| F10=y'                                                                 | у'                 | Complement   | Not y               |

| $F_{11} = x + y'$                                                      | х⊂у                | Implication  | If y then x         |

| $F_{12} = x'$                                                          | x                  | Complement   | Not x               |

| $\mathbf{F}_{13} = \mathbf{x}' + \mathbf{y}$                           | x⊃y                | Implication  | If x then y         |

| $F_{14} = (xy)'$                                                       | x†y                | NAND         | Not-AND             |

| $F_{15} = 1$                                                           |                    | Identity     | Binary constant 1   |

Table: 16 different logic operations with 2 binary variables

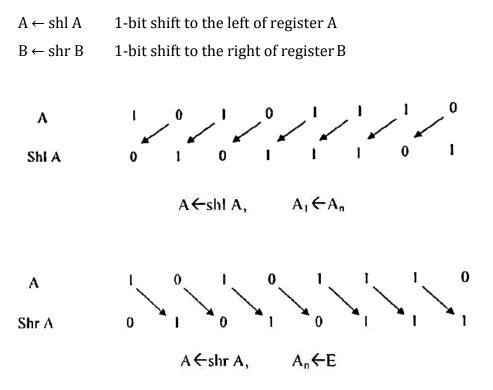

## Shift Micro-Operations

- Shift micro-operations shift the contents of a register either left or right.

- These micro- operations are generally used for serial transfer of data.

- They are also used along with arithmetic, logic, and other data-processing operations.

- No conventional symbol for shift operation. Here adopt symbols shl or shr

o shl - shift left

o shr - shift right

#### Example:

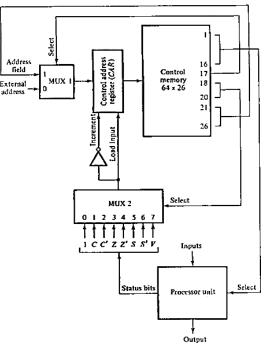

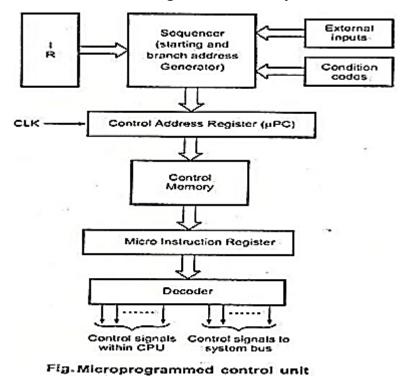

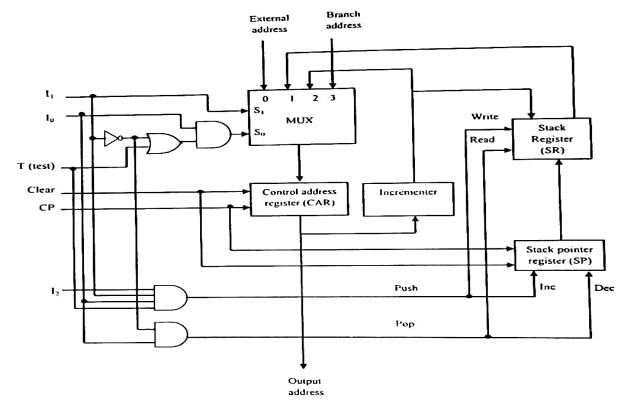

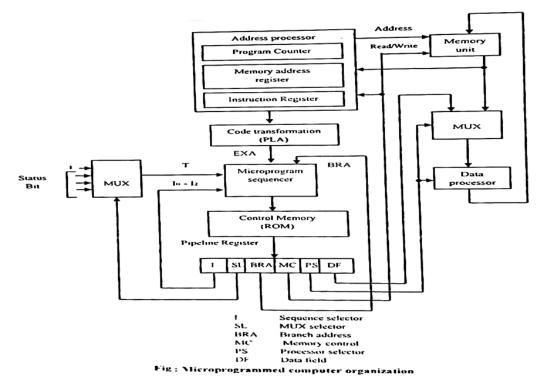

#### PROCESSOR LOGIC DESIGN

#### Processor Organization

- The processor part of a computer CPU is sometimes referred to as the data path of the CPU because the processor forms the paths for the data transfers between the registers in the unit.

- The various paths are said to be controlled by means of gates that open the required path and close all others.

- A processor unit can be designed to fulfill the requirements of a set of data paths for a specific application.

- In a processor unit, the data paths are formed by means of buses and other common lines.

- The control gates that formulate the given path are essentially multiplexers and decoders whose selection lines specify the required path.

- The processing of information is done by one common digital function whose data path can be specified with a set of common selection variables.

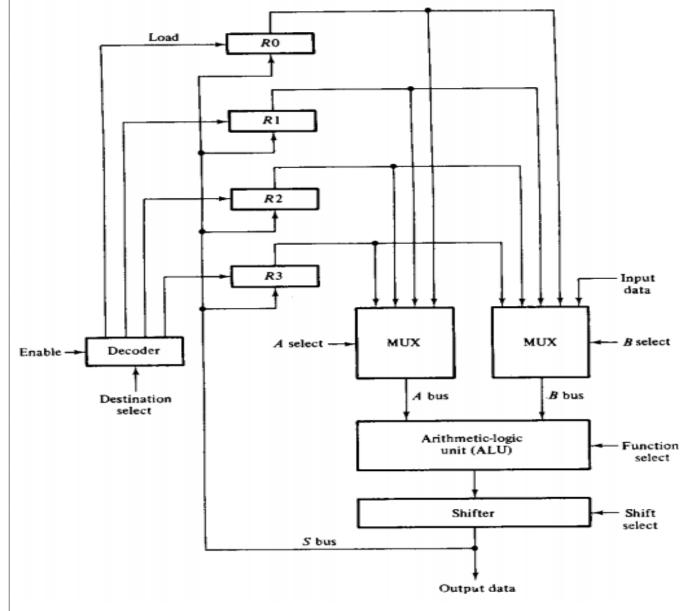

- A bus organization for four processor registers shown in below fig

JCET

- A bus organization for four processor registers is shown in Figure. Each register is connected to two multiplexers (MUX) to form input buses A and B.

- The selection lines of each multiplexer select one register for the particular bus.

- The A and B buses are applied to a common arithmetic logic unit.

- The function selected in the ALU determines the particular operation that is to be performed.

- The shift micro- operations are implemented in the shifter

- The result of the micro-operation goes through the output bus S into the inputs of all registers.

- The destination register that receives the information from the output bus is selected by a decoder.

- When enabled, this decoder activates one of the register load inputs to provide a transfer path between the data on the S bus and the inputs of the selected destination register.

- The output bus S provides the terminals for transferring data to an external destination.

- One input of multiplexer A or B can receive data from the outside.

- The control unit that supervises the processor bus system directs the information flow through the ALU by selecting the various components in the unit.

For example, to perform the microoperation:

## R1←R2+ R3

The control must provide binary selection variables to the following selector inputs:

- 1. *MUX A selector:* to place the contents of R2 onto bus A.

- 2. *MUX B selector*: to place the contents of R3 onto bus B.

- 3. *ALU function selector:* to provide the arithmetic operation A + B.

- 4. *Shift selector:* for direct transfer from the output of the ALU onto output bus S (no shift).

- 5. *Decoder destination selector*: to transfer the contents of bus S into R 1.

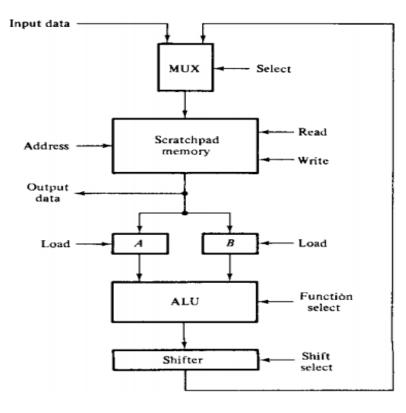

# Scratchpad memory

- The register in a processor unit can be enclosed in a small memory unit.

- When included in a processor unit, a small memory is sometime called a scratchpad memory.

- The use of a small memory is a cheaper alternative to collecting processor registers through a bus system.

- The difference between the two system is the manner in which information is selected for transfer into the ALU.

- In a bus system, the information transfer is selected by the multiplexer that form the buses.

- Processor unit that uses scratchpad memory is shown in figure. Resource register is selected from memory and loaded into register A.

- A Second source register is selected from memory and loaded into register B.

- The information in A and B is manipulated in the ALU and shifter.

JCET

- Result of the operation is transferred to a memory register specifying its word address and activating the memory-write input control.

- Assume that the memory has eight words, so that an address must be specified with three bits.

- To perform the operation  $R1 \leftarrow R2 + R3$

- The control must provide binary selection variable to perform the following sequence of microoperations

| $T_1: A \leftarrow M[010]$  | read R2 to register A |

|-----------------------------|-----------------------|

| T <sub>2</sub> : B ← M[011] | read R3 to register B |

$T_3: M[001] \leftarrow A + B$  perform operation in ALU and transfer result to R1

- Control function T<sub>1</sub> must supply an address of 010 to the memory and activate the read and load A inputs.

- Control function T<sub>2</sub> must supply an address 011 to the memory and activate the read and load B inputs.

Some processor employ a 2 port memory in order to overcome the delay caused when reading two source registers.

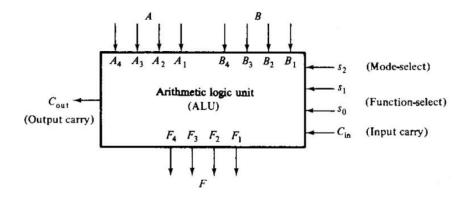

## Arithmetic Logic Unit

- An arithmetic logic unit (ALU) is a multi-operation, combinational-logic digital function.

- It can perform a set of basic arithmetic operations and a set of logic operations.

- The ALU has a number of selection lines to select a particular operation in the unit.

- The selection lines are decoded within the ALU so that k selection variables can specify up to 2<sup>k</sup> distinct operations.

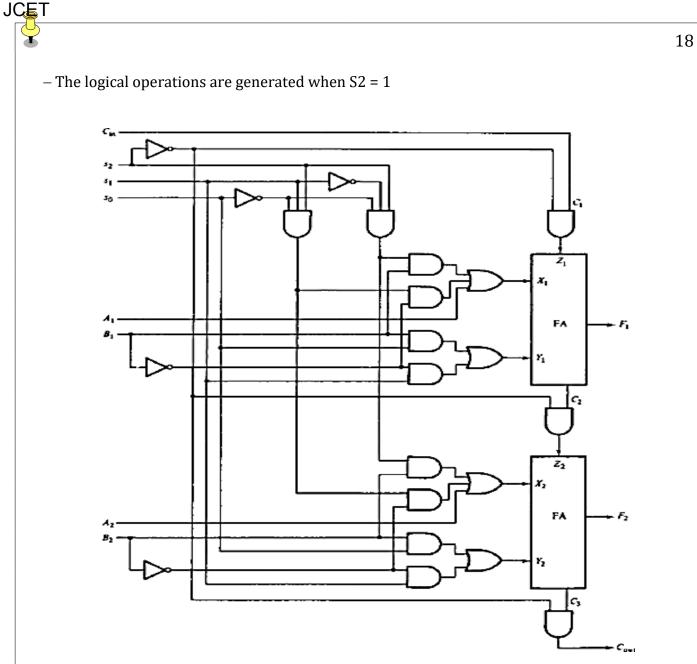

The figure shows the block diagram of 4 bit ALU.

- The 4 data input from A is combined with the input B to generate the output F.

- The Mode selection variable S2 is used to select either arithmetic operation or logic operation.

- The two function select input S1 and S0 specify the particular arithmetic or logic operation to be generated.

- The design of a typical ALU will be carried out in three stages.

- First, the design of the arithmetic section will be undertaken.

- Second, the design of the logic section will be considered.

- Finally, the arithmetic section will be modified so that it can perform both arithmetic and logic operations.

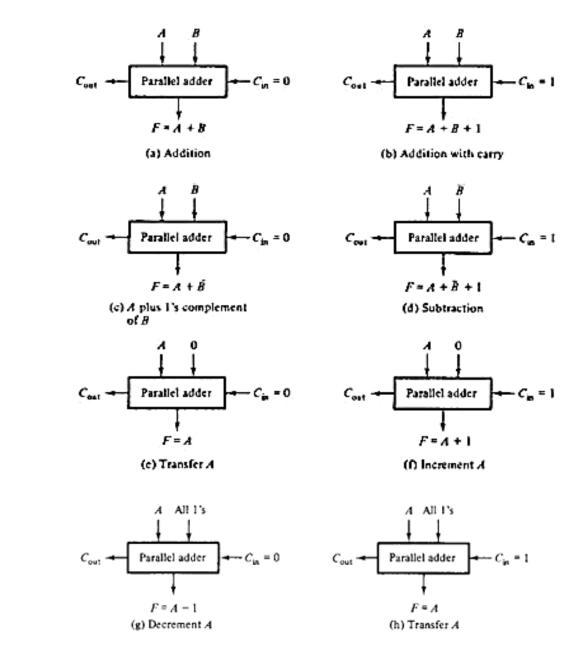

## > Design of Arithmetic Circuit

JCET

- The basic component of the arithmetic section of an ALU is a parallel adder.

- A parallel adder is constructed with a number of full-adder circuits connected in cascade.

- By controlling the data inputs to the parallel adder, it is possible to obtain different types of arithmetic operations.

The above figure demonstrates the arithmetic operations obtained when one set of inputs to a parallel adder is controlled externally.

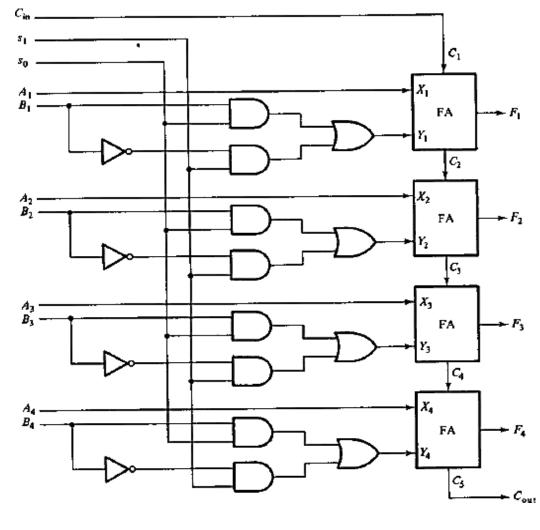

- The design of 4 bit arithmetic circuit that performs 8 arithmetic operations is shown in the figure.

- The number of bits in the parallel adder may be of any value.

JCET

- The input carry C<sub>in</sub> goes to the full-adder circuit in the least significant bit position.

- The output carry C<sub>out</sub> comes from the full-adder circuit in the most significant bit position.

- From the above Figure, by changing the B input and C<sub>in</sub> we get 8 operations. So the input B is applied in four different forms by using following circuit.

- The input A is applied directly to the 4-bit parallel adder and the input B is modified.

- The resultant arithmetic circuit is shown in below figure.

16

| Function                     | Output<br>equals        | Y<br>equals | Function<br>select |     |                |

|------------------------------|-------------------------|-------------|--------------------|-----|----------------|

|                              |                         |             | Cin                | \$0 | s <sub>1</sub> |

| Transfer A                   | F = A                   | 0           | 0                  | 0   | 0              |

| Increment A                  | F = A + 1               | 0           | 1                  | 0   | 0              |

| Add B to A                   | F = A + B               | В           | 0                  | I   | 0              |

| Add B to A plus 1            | F = A + B + 1           | B           | 1                  | 1   | 0              |

| Add 1's complement of $B$ to | $F = A + \overline{B}$  | B           | 0                  | 0   | 1              |

| Add 2's complement of B to   | $F = A + \tilde{B} + 1$ | Ē           | 1                  | 0   | 1              |

| Decrement A                  | F = A - 1               | All 1's     | 0                  | 1   | ī              |

| Transfer A                   | F = A                   | Ali l's     | 1                  | 1   | 1              |

- The function table for the arithmetic circuit is given below.

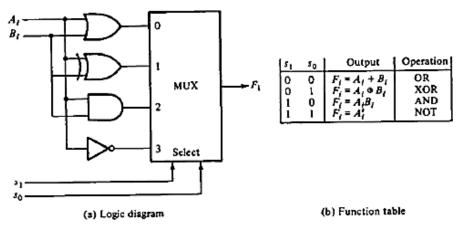

## > Design of Logic Circuit

- The logic microoperations manipulate the bits of the operands separately and treat each bit as a binary variable.

- The 16 logic operations can be generated in one circuit and selected by means of four selection lines. Since all logic operations can be obtained by means of AND, OR, and NOT (complement) operations, it may be more convenient to employ a logic circuit with just these operations.

- For three operations, we need two selection variables. But two selection lines can select among four logic operations, so we choose also the exclusive-OR (XOR) function for the logic circuit to be designed in this and the next section.

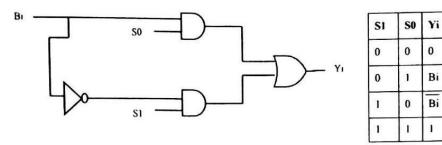

- The simplest and most straight forward way to design a logic circuit is shown in figure given below.

The diagram shows one typical stage designated by subscript i.

- The circuit must be repeated n times for an n-bit logic circuit.

- The four gate generate four logic operations OR, XOR, AND, and NOT.

- The two selection variables in the multiplexer select one of the gates for the output.

- The function table lists the output logic generated as a function of the two selection variables.

- The logic circuit can be combined with the arithmetic circuit to produce one arithmetic logic unit.

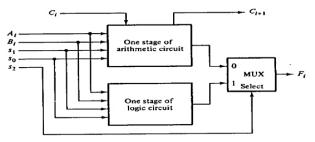

- This is illustrated in the below figure

- We use a third selection variable, S<sub>2</sub>, to differentiate between arithmetic logic circuit.

- When  $S_2 = 0$ , the arithmetic output is selected, when  $S_2 = 1$ , the logic output is selected.

- Although the two circuits can be combined in this manner, this is not the best way to design an ALU.

- The logic circuit can be combined with the arithmetic circuit to produce one arithmetic logic unit.

Design steps

1. Design the arithmetic section independent of the logic section.

2. Determine the logic operations obtained from the arithmetic circuit in step 1, assuming that the input carries to all stages are 0.

3. Modify the arithmetic circuit to obtain the required logic operations.

- The inputs to each full-adder circuit are specified by the Boolean functions:

$$\begin{split} X_{i} &= A_{i} + S_{2} S_{1}' S_{0}' B_{i} + S_{2} S_{1} S_{0}' B_{i} \\ Y_{i} &= S_{0} B_{i} + S_{1} B_{i}' \\ Z_{i} &= S_{2}' C_{i} \end{split}$$

– When S2 = 0, the three functions reduce to:

$$\begin{split} X_i &= A_i \\ Y_i &= S_0 \; B_i + S_1 \; B_i \\ Z_i &= C_i \end{split}$$

– Which are the functions for the arithmetic circuit.

17

– The function table for the Arithmetic and Logic Unit is shown below

| Selection      |     |                       |                 |                    |                      |

|----------------|-----|-----------------------|-----------------|--------------------|----------------------|

| s <sub>2</sub> | 51  | <i>s</i> <sub>0</sub> | C <sub>in</sub> | Output             | Function             |

| 0              | 0   | 0                     | 0               | F = A              | Transfer A           |

| Ō              | 0   | 0                     | 1               | F = A + 1          | Increment A          |

| 0              | Ō   | 1                     | 0               | F = A + B          | Addition             |

| õ              | Ō   | ī                     | 1               | F = A + B + 1      | Add with carry       |

| õ              | ĩ   | Ō                     | Ō               | F = A - B - 1      | Subtract with borrow |

| õ              | 1   | 0                     | 1               | F = A - B          | Subtraction          |

| Ô.             | 1   | i                     | 0               | F = A - 1          | Decrement A          |

| õ              | 1   | ī                     | ĩ               | F = A              | Transfer A           |

| ĩ              | · 0 | Ō                     | X               | $F = A \lor B$     | OR                   |

| i              | õ   | ĩ                     | X               | $F = A \oplus B$   | XOR                  |

| î              | ĩ   | Ō                     | X               | $F = A \wedge B$   | AND                  |

| 1              | 1   | 1                     | x               | $F = \overline{A}$ | Complement A         |

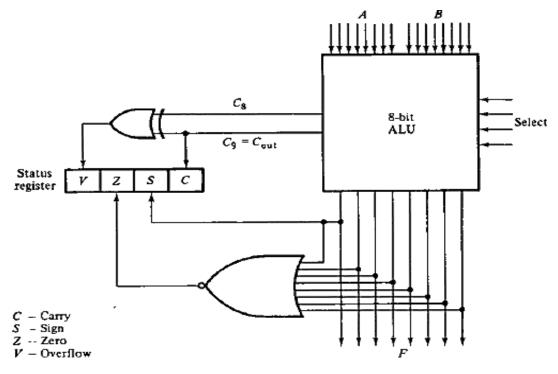

### Status Registers

- The status register is the hardware register that contains information about the state of the processor.

- The relative magnitude of two numbers may be determined by subtracting one number from the other and then checking certain bit conditions in the resultant difference.

- This status bit conditions (often called condition-code bits or flag bits) are stored in a status register.

- Status register is a 4 bit register.

- The four bits are C (carry), Z (zero), S (sign) and V (overflow).

- These bits are set or cleared as a result of an operation performed in the ALU.

- Bit C is set if the output carry of an ALU is 1.

- Bit S is set to 1 if the highest order bit of the result in the output of the ALU is 1.

- Bit Z is set to 1 if the output of the ALU contains all O's.

- Bit V is set if the exclusive —OR of carries C8 and C9 is 1, and cleared otherwise. This is the condition for overflow when the numbers are in signed 2's complement representation. For an 8 bit ALU, V is set if the result is greater than 127 or less than -128.

After an ALU operation, status bits can be checked to determine the relationship that exist between the values of A and B.

19

- C-carry: Bit C is set if the output carry of the ALU is 1. It is cleared if the output carry is 0.

- S-sign bit: Bit S is set if the highest order of the result in the output of the ALU is 1. It is cleared if the highest order bit is 0.

- Z-zero: Bit Z is set if the output of the ALU contains 0's and cleared otherwise. Z=1 if the result is zero and Z=0 if result is nonzero

- V-overflow: set if there is any overflow, for a 8 bit ALU, V is set if the result is greater than 127 and less than -128.

- Relative magnitudes of A and B can be checked by compare operation.

- If A-B is performed for two unsigned binary numbers, relative magnitudes of A and B can be determined from the values transferred to the C and Z bits. If Z=1,we knows that A=B, since A-B=0. If Z=0, then we know that A is not equal to B. Similarly C=1 if A>=B and C=0 if A<B. The following table lists the various conditions</li>

| Relation   | Condition of<br>status bits | Boolean<br>function |

|------------|-----------------------------|---------------------|

| A > B      | C = 1 and $Z = 0$           | CZ'                 |

| $A \ge B$  | C = 1                       | С                   |

| A < B      | C = 0                       | C'                  |

| $A \leq B$ | C = 0 or $Z = 1$            | C' + Z              |

| A = B      | Z = 1                       | Ζ                   |

| $A \neq B$ | Z = 0                       | Z                   |

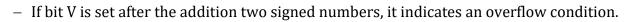

## > Design of Combinational Logic Shifter

- The shift unit attached to the processor transfers the output of the ALU onto the output bus.

- Shifter may function in four different ways.

- 1. The shifter may transfer the information directly without a shift.

- 2. The shifter may shift the information to the right.

- 3. The shifter may shift the information to the left.

- 4. In some cases no transfer is made from ALU to the output bus.

- A shifter is a bi-directional shift-register with parallel load.

- The information from ALU can be transferred to the register in parallel and then shifted to the right or left.

- In this configuration, a clock pulse is needed for the transfer to the shift register, and another pulse is needed for the shift.

- Another clock pulse may also in need of when information is passed from shift register to destination register

- The number of clock pulses may reduce if the shifter is implemented with a combinational circuit.

- A combinational—logic shifter can be constructed with multiplexers. The above figure will show the same.

- $\,$  Shifter operation can be selected by two variables  $H_1\,H_0$

- If  $H_1 H_0 = 0 \ 0$  No shift is executed and the signal from F go directly to S lines

- If  $H_1 H_0 = 0.1$  Shift Right is executed

- If  $H_1 H_0 = 1.0$  Shift Left is executed

- If  $H_1 H_0 = 1 1$  No operations

JCET

## Design of Accumulator

- Some processor units distinguish one register from all others and call it an accumulator register.

- An accumulator is a register for short-term, intermediate storage of arithmetic and logic data in a computer's CPU

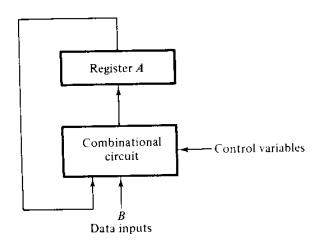

- The block diagram of an accumulator that forms a sequential circuit is shown in figure below.

- The A register and the associated combinational circuit constitutes a sequential circuit.

- The combinational circuit replaces the ALU but cannot be separated from the register, since it is only the combinational-circuit part of a sequential circuit.

- The A register is referred to as the accumulator register and is sometimes denoted by the symbol AC.

- Here, accumulator refers to both the A register and its associated combinational circuit.

- The external inputs to the accumulator are the data inputs from B and the control variables that determine the micro operations for the register.

- The next state of register A is a function of its present state and of the external inputs.

- An Accumulator can performs Parallel load, Shift operations, Counting, and Data-processing operations

|   |            |   |            | Function of selection variables |            |                                |                        |                        |  |  |

|---|------------|---|------------|---------------------------------|------------|--------------------------------|------------------------|------------------------|--|--|

|   | ina<br>ode | - | А          | В                               | D          | $F \text{ with} \\ C_{in} = 0$ | F with<br>$C_{in} = 1$ | Н                      |  |  |

| 0 | 0          | 0 | Input data | Input data                      | None       | A, C ← 0                       | A + 1                  | No shift               |  |  |

| 0 | 0          | 1 | RI         | <i>R</i> 1                      | R1         | A + B                          | A + B + l              |                        |  |  |

| 0 | 1          | 0 | R2         | R2                              | R2         | A - B - 1                      | A - B                  | Shift-left, $I_L = 0$  |  |  |

| 0 | 1          | 1 | R3         | R3                              | R3         | A = 1                          | A, C ← 1               | 0's to output bus      |  |  |

| 1 | 0          | 0 | R4         | R4                              | R4         | $A \lor B$                     |                        |                        |  |  |

| 1 | 0          | 1 | R5         | R5                              | R5         | $A \oplus B$                   | _                      | Circulate-right with C |  |  |

| 1 | 1          | 0 | R6         | R6                              | R6         | $A \wedge B$                   | _                      | Circulate-left with C  |  |  |

| 1 | 1          | 1 | R7         | R7                              | <b>R</b> 7 | Ā                              |                        | _                      |  |  |

- The micro operations included in an accumulator depend on the operations that must be included in the particular processor.

- The set of micro operations for the accumulator is given in table

JCET

- In all listed microoperations A is the source register. B register is used as the second source register.

- The destination register is also accumulator register itself. For a complete accumulator there will be n stages.

- The inputs and outputs of each stage can be connected in cascade to form a complete accumulator.

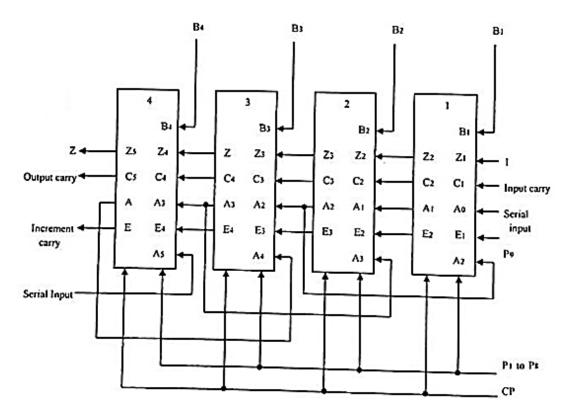

- Here we are discussing the design of a 4 bit accumulator.

- The number on top of each block represents the bit position.

- All blocks receive 8 control variables P1 to P8 and the clock pulses from CP.

- The other six inputs and four outputs are same as with the typical stage.

- The zero detect chain is obtained by connecting the z variables in cascade, with the first block receiving a binary constant I.

- The last stage produces the zero detect variable Z.

- Total number of terminals in the 4 bit accumulator is 25, including terminals for the A outputs.

- Incorporating two more terminals for power supply, the circuit can be enclosed within one IC package having 27 or 28 pins.

- The number of terminals for the control variable can be reduced from 9 to 4 if a decoder is inserted in the IC.

- In such cases, IC pin count is also reduced to 22 and the accumulator can be extended to 16

microoperations without adding external pins (That is, with 4 bits we can identify 16 operations).

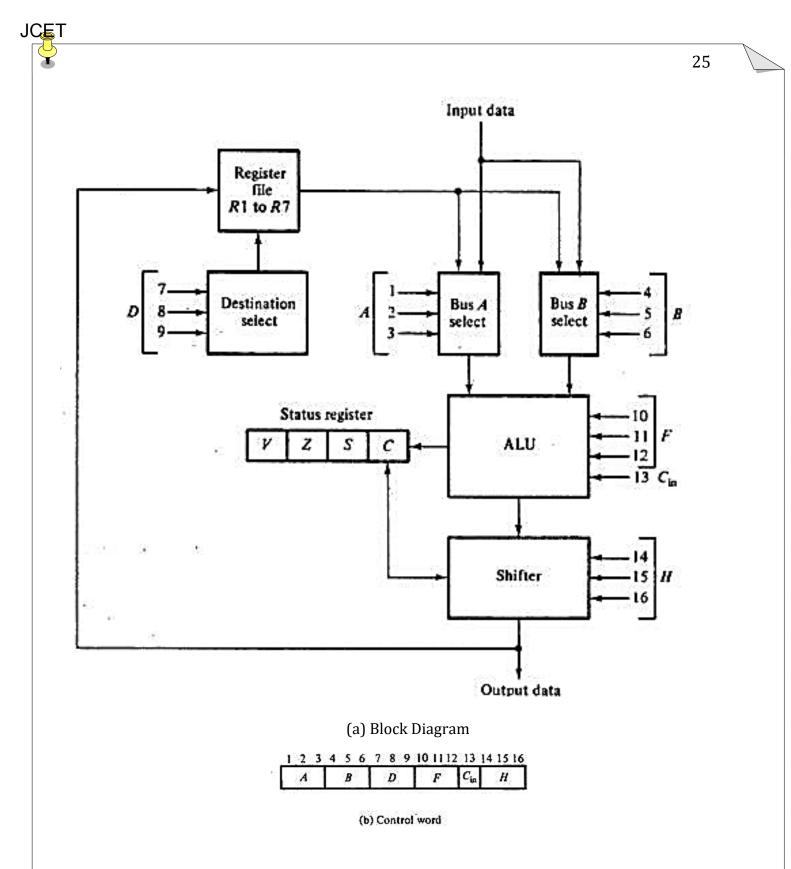

# Processor Unit

- A block diagram of a processor unit is shown in figure.

- It consists of seven registers R1 through R7 and a status register.

- The outputs of the seven registers go through two multiplexers to select the inputs to the ALU.

- Input data from an external source are also selected by the same multiplexers. The output of the ALU goes through a shifter and then to a set of external output terminals.

- The functions of all selection variables are specified in table below.

- The 3-bit binary code listed in the table specifies the code for each of the five fields A, B, D, input data, F, and H.

- The register selected by A, B, and D is the one whose decimal number is equivalent to the binary number in the code.

- When the A or B field is 000, the corresponding multiplexer selects the input data. When D = 000, no destination register is selected.

| $\begin{array}{ccc} p_1 & A \leftarrow A + B \\ p_2 & A \leftarrow 0 \end{array}$ | Add                    |

|-----------------------------------------------------------------------------------|------------------------|

| 4 0                                                                               | <u>C</u> 1             |

| $p_2 \qquad A \leftarrow 0$                                                       | Clear                  |

| $p_3 \qquad A \leftarrow \overline{A}$                                            | Complement             |

| $p_4 \qquad A \leftarrow A \land B$                                               | AND                    |

| $p_5 \qquad A \leftarrow A \lor B$                                                | OR                     |

| $p_6 \qquad A \leftarrow A \oplus B$                                              | Exclusive-OR           |

| $p_7 \qquad A \leftarrow \operatorname{shr} A$                                    | Shift-right            |

| $p_8 \qquad A \leftarrow \text{shl } A$                                           | Shift-left             |

| $p_9 \qquad A \leftarrow A + 1$                                                   | Increment              |

| If $(A = 0)$ then                                                                 | (Z = 1) Check for zero |

- The three bits in the F field, together with the input carry C<sub>in</sub>, provide the 12 operations of the ALU as specified in above table.

- Note that there are two possibilities for F = A. In one case the carry bit C is cleared, and in the other case it is set to 1.

25

# **MODULE – III**

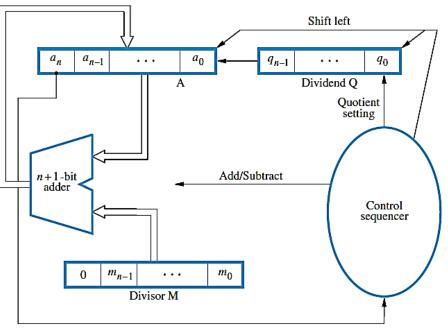

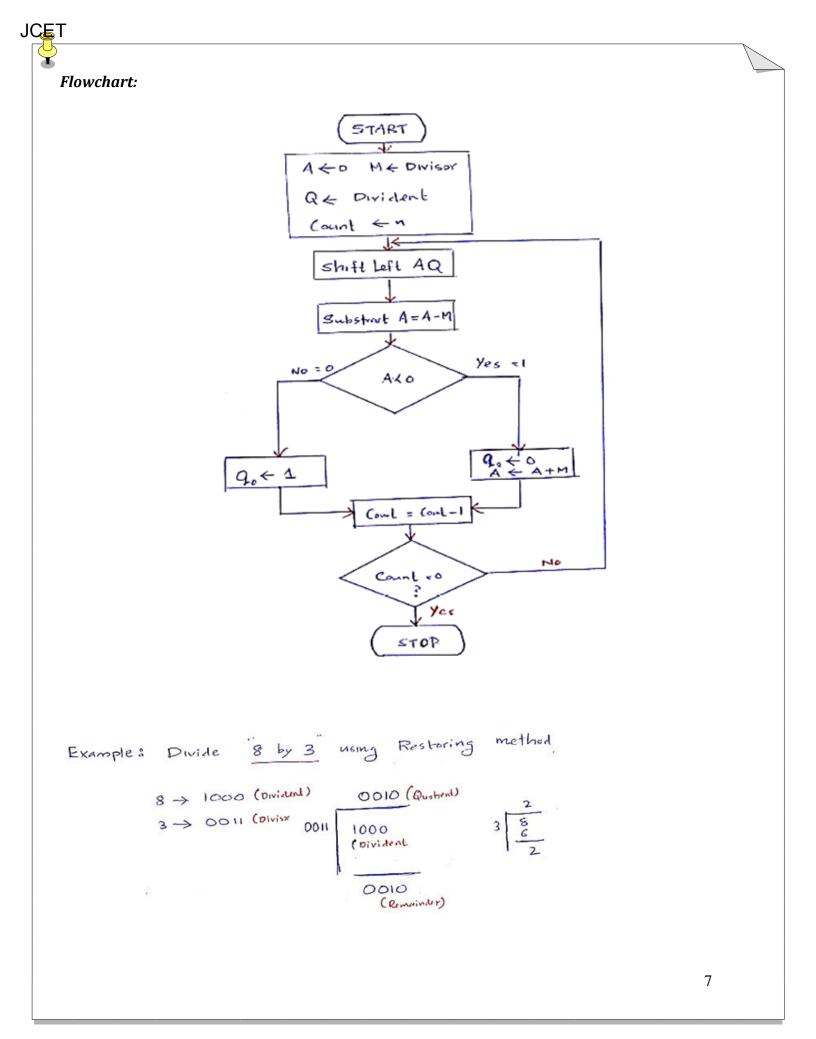

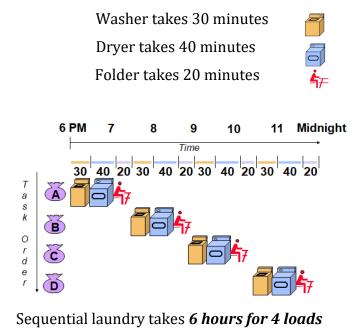

*Arithmetic algorithms:* Algorithms for multiplication and division (restoring method) of binary numbers. Array multiplier, Booth's multiplication algorithm.

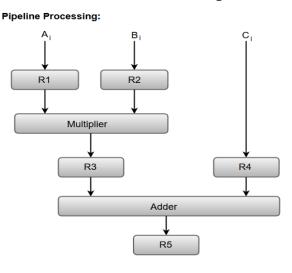

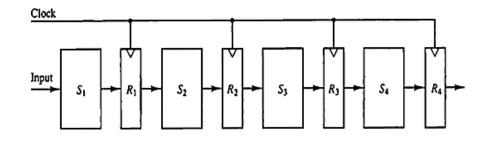

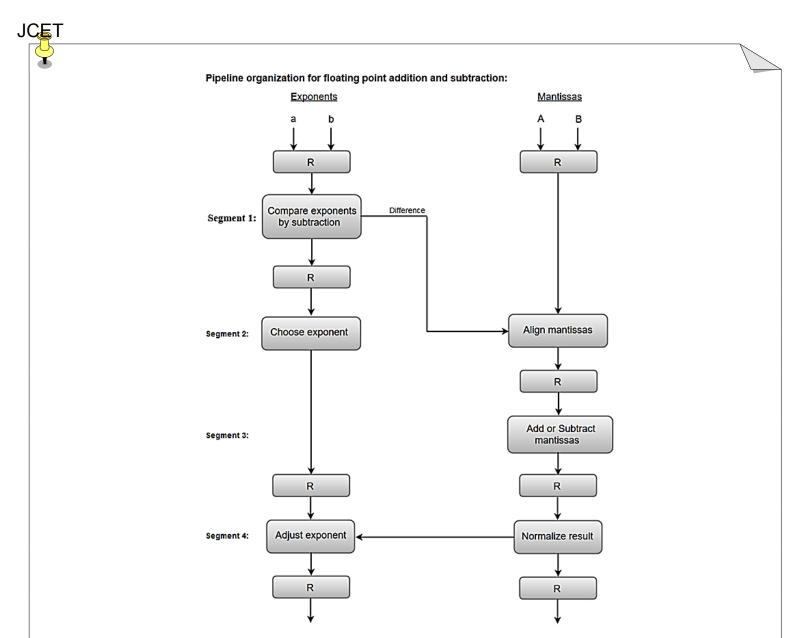

**Pipelining:** Basic principles, classification of pipeline processors, instruction and arithmetic pipelines (Design examples not required), hazard detection and resolution.

#### **ARITHMETIC ALGORITHMS**

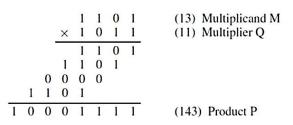

#### 1. Multiplication of binary numbers

- In the binary system, multiplication of the multiplicand by one bit of the multiplier is easy.

- If the multiplier bit is 1, the multiplicand is entered in the appropriate shifted position.

- If the multiplier bit is 0, then Os are entered, as in the third row of the example.

- The product is computed one bit at a time by adding the bit columns from right to left and propagating carry values between columns.

#### **Array Multiplier**

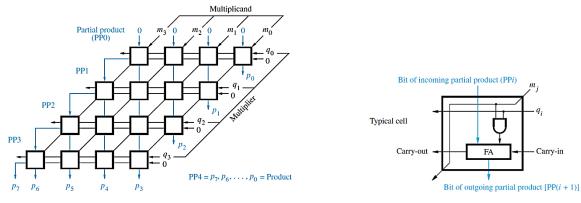

- Binary multiplication of unsigned operands can be implemented in a combinational, two dimensional logic array, as shown in Figure for the 4-bit operand case.

- The main component in each cell is a full adder, FA. The AND gate in each cell determines whether a multiplicand bit, m<sub>j</sub>, is added to the incoming partial-product bit, based on the value of the multiplier bit, q<sub>i</sub>.

- Each row i, where  $0 \le i \le 3$ , adds the multiplicand (appropriately shifted)to the incoming partial product, PPi, to generate the outgoing partial product, PP(i + 1), ifqi = 1. If qi = 0, PPi is passed vertically downward unchanged.

- PP0 is all 0s, and PP4 is the desired product.

- The multiplicand is shifted left one position per row by the diagonal signal path.

- We note that the row-by-row addition done in the array circuit differs from the usual hand addition described previously, which is done column-by-column.

(a)Array multiplication of positive binary operands

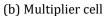

## Hardware:

JCET

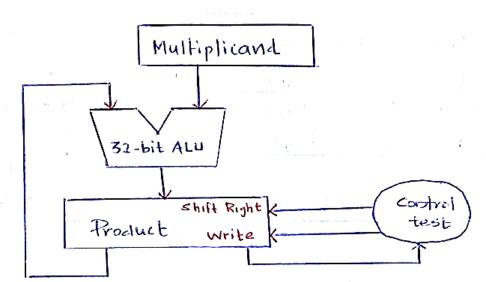

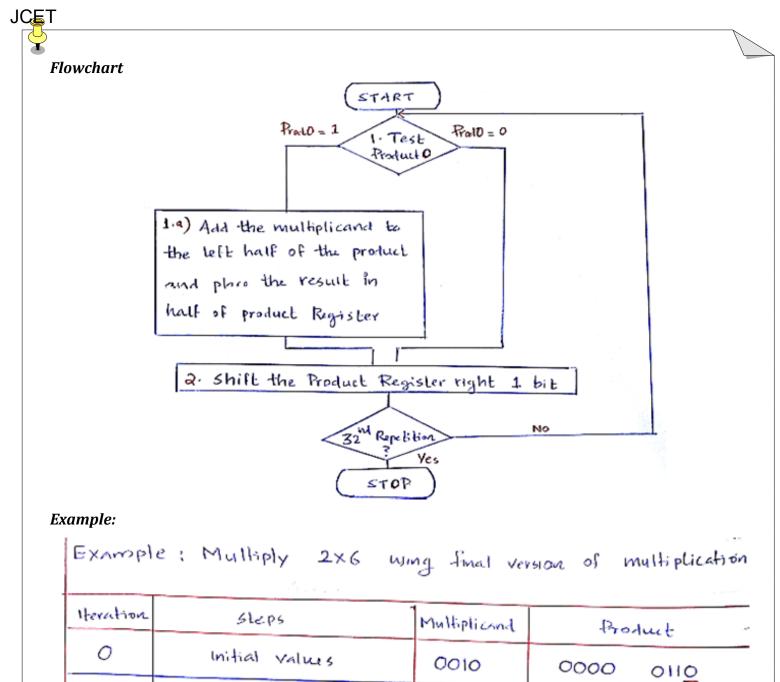

| eration | Steps                                             | Multiplicand | Broduct   |

|---------|---------------------------------------------------|--------------|-----------|

| 0       | Initial Values                                    | 0010         | 0000 0110 |

| L       | 1a: no operation<br>2: shift freduct Right        | 0010         | 0000 0110 |

| Ş       | 2a: Prod = Prod + Manl<br>Q: shift Product Right  | 0010         | 0010 0011 |

| 3       | 1a: Prod = Brod + Mand<br>R: Shift Brailuit Reght | 0010         | 0001 1000 |

| 4       | 2: Shift Brodul Right                             | 0010         | 0001 1000 |

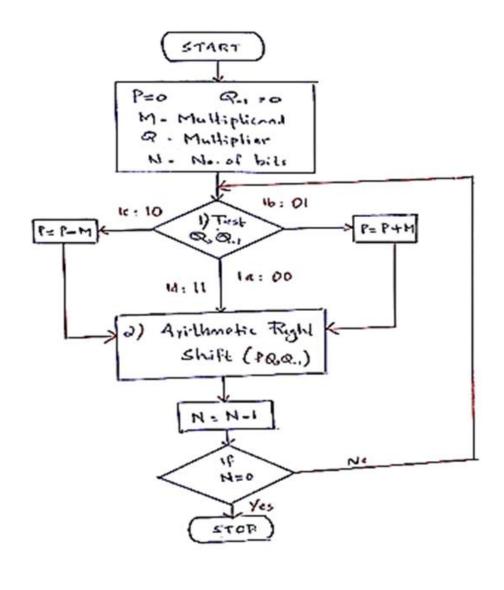

# **Booth's Multiplication Algorithm**

- Booth's algorithm is a powerful direct algorithm to perform signed number multiplication.

- The algorithm is based on the fact that any binary number can be represented by the sum and difference of other binary numbers.